Filter Design HDL Coder erzeugt synthetisierbaren, portierbaren VHDL® und Verilog® -Code zum Implementieren von Fixpunkt-Filtern, die mit MATLAB in FPGAs oder ASICs erstellt wurden. Es werden automatisch VHDL- und Verilog-Testbenches erstellt, die zum Simulieren, Testen und Verifizieren des generierten Codes verwendet werden können.

Jetzt beginnen:

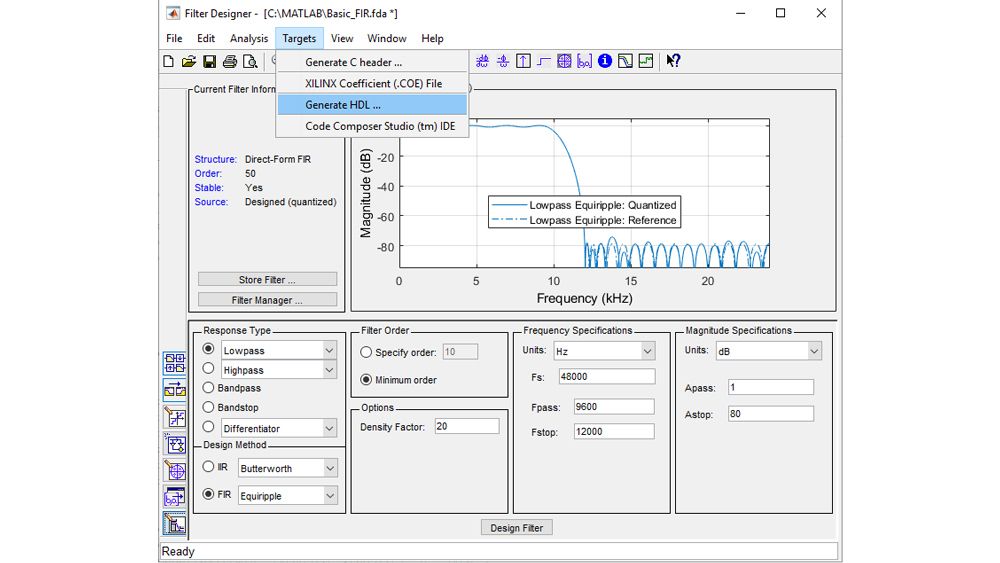

Filter Design HDL Coder wurde in die DSP System Toolbox integriert, um Design und Implementierungsumgebung zu vereinheitlichen. Das Entwerfen von Filtern bzw. das Erstellen von VHDL- und Verilog-Code kann entweder über die MATLAB-Befehlszeile oder in DSP System Toolbox erfolgen. Dabei werden die Apps „Filter Design and Analysis“ oder „Filter Builder“ verwendet.

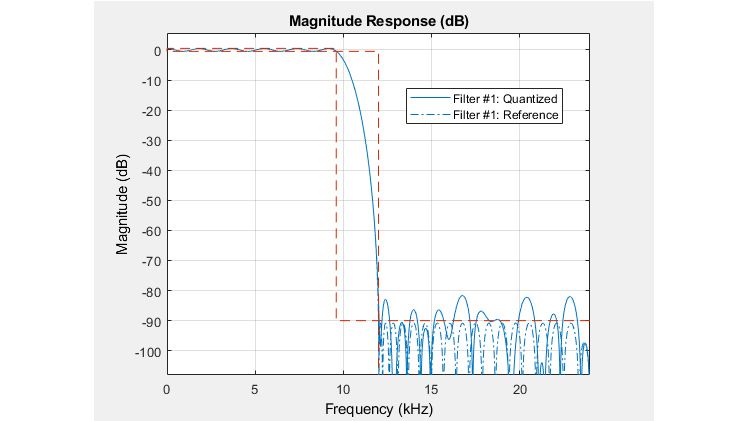

Die Eingabe für den Entwurf in Filter Design HDL Coder ist ein quantisierter Filter, den Sie auf zweierlei Wegen erstellen können:

- Filter mittels DSP System Toolbox entwerfen und quantisieren

- Entwerfen Sie den Filter in der Signal Processing Toolbox und quantisieren Sie diesen anschließend mit DSP System Toolbox

Filter Design HDL Coder unterstützt zahlreiche bedeutende Filterstrukturen, unter anderem:

Zeitdiskrete endliche Impulsantwort (FIR, Finite Impulse Response), die symmetrische, anti-symmetrische und transponierte Strukturen beinhaltet

Second-Order Section (SOS) mit unendlicher Impulsantwort (Infinite Impulse Response, IIR), die direkte Strukturen der Form I und II sowie transponierte Strukturen umfasst

Multiraten-Filter, die Strukturen für kaskadierte Integrator-Comb (CIC) Interpolatoren und Decimatoren, Direct-Form FIR und transponierte FIR Polyphase-Interpolatoren und Decimatoren, FIR Hold- und Linear-Interpolatoren sowie FIR Polyphasen-Abtastratenwandler umfassen

Fractional Delay-Filter, inklusive Farrow-Strukturen

Filter Design HDL Coder kann HDL-Code aus kaskadierten Multiraten-Filtern und zeitdiskreten Filtern erstellen. Jede dieser Einzelraten- und Multiraten-Filterstrukturen unterstützt die Umsetzung über Festkomma- und Gleitkomma-Arithmetik (doppelte Genauigkeit). Zusätzlich unterstützen die FIR-Strukturen vorzeichenlose Festkomma-Koeffizienten.

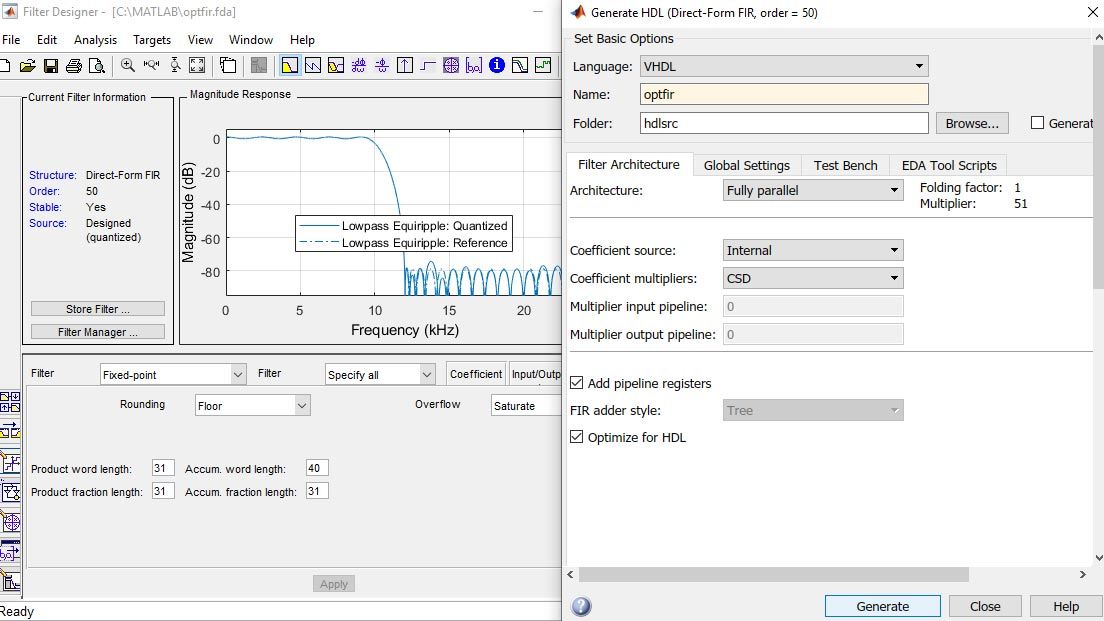

Der VHDL- und Verilog-Code für Festkomma-Filter kann entweder über die App „Filter Design and Analysis“ oder „Filter Builder“ generiert werden. In beiden Apps können Sie beim Erstellen des HDL-Codes Optionen festlegen, welche die Implementierungsarchitektur bestimmen, Port-Datentypen wählen, Pipeline-Register einfügen, und mehr. Über weitere Optionen können Sie eine Testumgebung für den HDL-Entwurf Ihres Filters erstellen und konfigurieren.

Filter Design HDL Coder generiert HDL-Code für Filter und die Testbench eines quantisierten Filters anhand einer gewählten Option, eines Eigenschaftsnamens und Eigenschaften-Wertepaars. In diesen Einstellungen können Sie:

- Sprachelemente benennen

- Port-Parameter festlegen

- Erweiterte Funktionen zur HDL-Codegenerierung anwenden

Alle Eigenschaften haben Standardeinstellungen. Sie können die HDL-Ausgabe anpassen, indem Sie die Einstellungen in der App „Filter Design and Analysis“ oder „Filter Builder“ konfigurieren. In den Apps können Sie Eigenschaften festlegen, die verknüpft sind mit:

- HDL-Sprachspezifikationen

- Spezifikationen für Dateiname und Position

- Reset-Spezifikationen

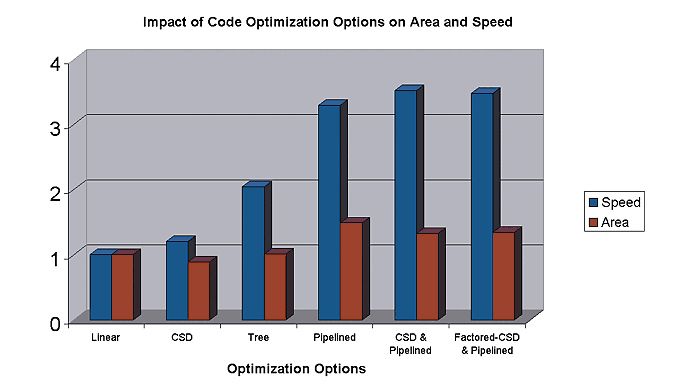

- Optimierungen des HDL-Codes

- Anpassungen der Testbench

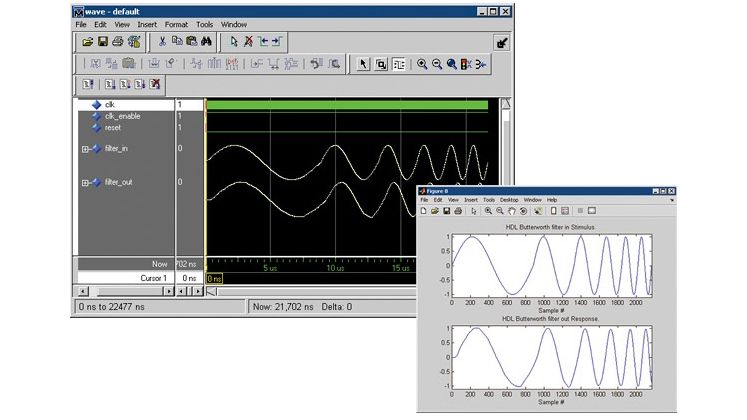

Sie können eine VHDL- oder Verilog-Testbench zum Simulieren und Testen des generierten HDL-Codes erstellen. Außerdem können Sie mit HDL Verifier einen Block zur Co-Simulation mit Simulink erstellen, um Ihr verhaltensbasiertes Filtermodell sowie die in Simulink laufenden Tests mit dem generierten HDL-Code zu verknüpfen, der in den Simulatoren Cadence® Incisive® und Xcelium™ bzw. Mentor® ModelSim® und Questa® ausgeführt wird. Eine Co-Simulation vereinfacht die Verifikation Ihres Filterentwurfs, indem Sie die Ergebnisse aus dem generierten HDL-Code und jene aus dem in Simulink ausgeführten, verhaltensbasierten Filtermodell direkt miteinander vergleichen können. Durch diese Integration können Sie die fortschrittlichen Analyse- und Visualisierungsfunktionen von MATLAB and Simulink zum Testen, Debuggen und Verifizieren der HDL-Implementierung Ihrer Filterentwürfe nutzen.